24小時聯系電話:18217114652、13661815404

中文

行業資訊

高速電路設計信號完整性分析

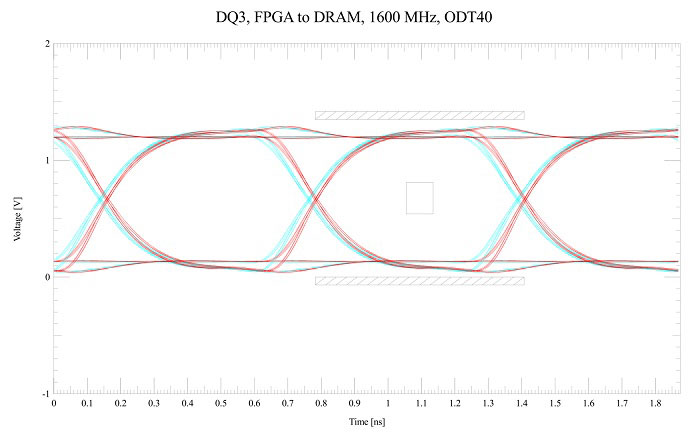

在高速電路設計中,元件和元件封裝可能影響芯片內以及PCB的信號完整性。實際上,信號完整性包括一組確定信號質量的測量值,作為分析和減輕噪聲,失真和損耗影響的一種方法。這是一組設計實踐和測試,有兩個常見的信號完整性電路設計問題,即信號的時序和質量。信號應按預期到達目的地嗎?到達那里后狀況?

在高速電路設計項目中,信號完整性(SI)是獲得設計成功的必備條件。因此我司會對設計的電路板進行信號完整性分析,以確保產品完整性和無故障高速電路設計。而我們的信號完整性分析如下:

1、布線前后的高速信號完整性分析和仿真

2、28GHz +收發器和40GHz +封裝級仿真

3、信號完整性驅動的層堆棧和約束生成

4、針對復雜拓撲的網絡調度和設計優化,例如多點總線(DDR3,DDR4)

5、減少反射和串擾,以改善時序裕度和發射

6、優化去耦,實現電源完整性和較低成本

7、同時考慮開關噪聲和設計策略

8、組件和系統特性,包括完整的S參數,增益和噪聲系數優化

9、針對敏感信號和監管批準的屏蔽設計和分離平面優化

10、比吸收率(SAR)分析

上海韜放電子提供專業的高速電路設計服務,如果您有這方面的需求,請與我們聯系。